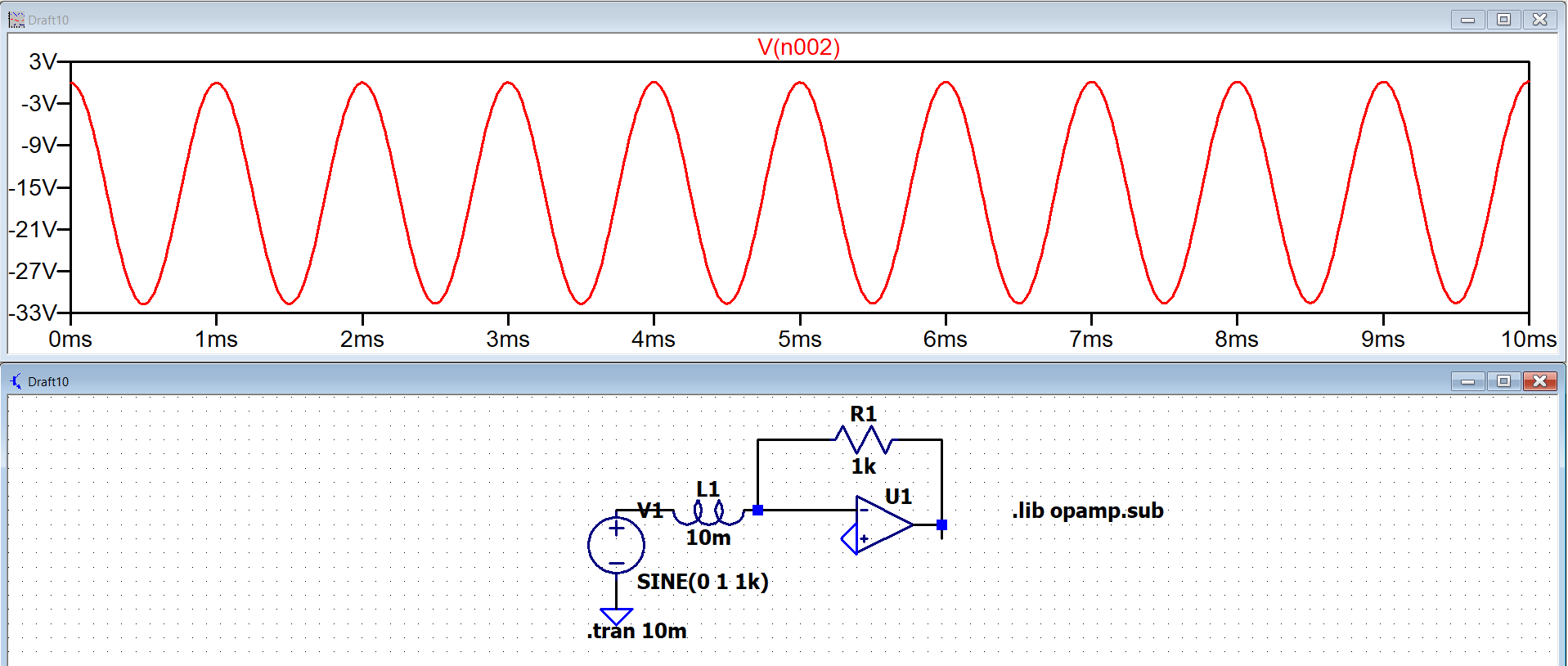

The actual issue is that LTspice assumes the wrong value for its initial conditions. You need to remember that the current in an inductor is 90° out of phase with the voltage across it (ignoring the effect of the ESR of the inductor for the moment).

Therefore, when voltage across it is zero, the current will be non-zero. LTspice starts it zero, which can't be correct. In the simple case of your schematic, you can calculate when the initial current should be, and initialise the inductor current to that. Add the following to your schematic to correctly initialise the inductor current, and then it all behaves as expected.

.param Iinit 1/(2 * pi * 1k)/10m

.ic I(L1)={Init}